### **APPLICATION NOTE**

A wideband 30 W push-pull amplifier with two MOS transistors BLF244 ( $V_{DS}$  = 28 V); range 25 – 110 MHz

NCO8701

### **CONTENTS**

| 1                        | INTRODUCTION                                                                                                       |

|--------------------------|--------------------------------------------------------------------------------------------------------------------|

| 2                        | AMPLIFIER DESIGN                                                                                                   |

| 2.1<br>2.2<br>2.3<br>2.4 | General Powergain, input- and output impedance Output matching section Input matching section                      |

| 3                        | TRANSFORMER DESIGN                                                                                                 |

| 3.1<br>3.2<br>3.3<br>3.4 | General Design of the output transformer Design of the input transformer The tapped choke (T2)                     |

| 4                        | AMPLIFIER CONSTRUCTION                                                                                             |

| 4.1<br>4.2               | Printed circuit board and component layout Heatsink                                                                |

| 5                        | AMPLIFIER ALIGNMENT                                                                                                |

| 6                        | AMPLIFIER PERFORMANCE                                                                                              |

| 6.1<br>6.2<br>6.3<br>6.4 | General Performance at constant output power Performance at constant input power Performance at constant frequency |

| 7                        | CONCLUSIONS                                                                                                        |

| 8                        | REFERENCES                                                                                                         |

### Application Note NCO8701

#### 1 INTRODUCTION

A wideband push-pull power amplifier has been developed for the frequency range 25-110 MHz. The design is based on the BLF244, a silicon N-channel enhancement mode vertical D-MOS transistor designed for large-signal amplifier applications in the VHF range. This device can deliver 15 W output power at 175 MHz when operated from a 28 V supply. The transistor has a 4-lead flange envelope with a ceramic cap (SOT123).

The objective was to design and construct a 30 W wideband amplifier with high gain and efficiency and low input VSWR and second order distortion. With respect to gain and efficiency a reasonable flatness was desired. The push-pull design is employed because of its low second order distortion.

The design and practical realization of this amplifier are described in the following chapters.

#### 2 AMPLIFIER DESIGN

#### 2.1 General

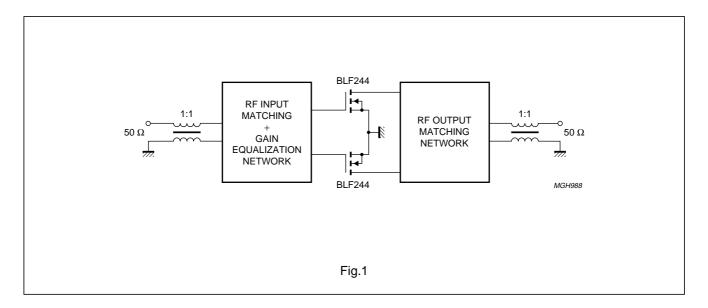

The schematic set up of the amplifier is depicted in Fig.1.

Two 1: 1 balance to unbalance transformers are applied; one for splitting the single-ended input source into two out of phase sources driving the transistor-inputs, the other for adding the outputs from the transistors.

Transmission line transformers are employed because of there excellent broadband response. These transformers consist of a twisted-wire-pair transmission line wound on a ferrite toroid.

At the input side a special matching network is applied to obtain a low VSWR and compensation for variation in gain with frequency.

The matching network at the output side provides the transistors with the optimum load for an output power of 30 W at  $V_{DS} = 28 \text{ V}$ .

### 2.2 Powergain, input- and output impedance

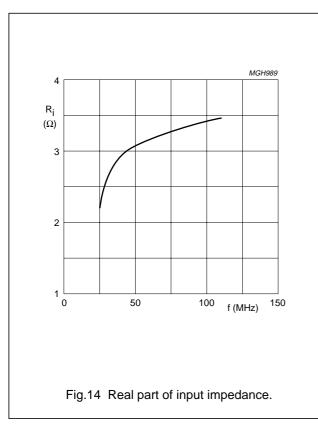

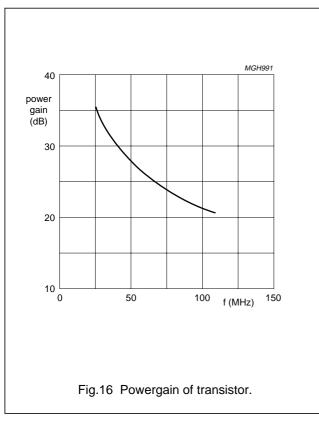

The design has been started by determining powergain, input impedance and output impedance of the transistor for the frequency range 25-110 MHz.

First the output impedance was determined.

For HF and VHF the optimum load resistance RL can be calculated with reasonable accuracy with the formula:

### Application Note NCO8701

For  $V_{DS}$  = 28 V and  $P_{O}$  = 15 W we get:  $R_{L}$  = 26.1  $\Omega$ .

The output impedance is the parallel combination of the output capacitance  $C_O$  of the transistor and the optimum load resistance.

Because of the large drain voltage swing the effective output capacitance  $C_O$  is approx. 15% higher than the value of  $C_{OSS}$ . For BLF244  $C_{OSS}$  is typical 38 pF, so  $C_O$  is equal to 43.7 pF. So the output impedance of this transistor can be represented by 26.1  $\Omega$ //43.7 pF for the whole frequency range.

Second the large-signal input impedance and powergain versus frequency were determined by measurement. For this purpose a single-ended test amplifier was constructed. This amplifier was matched at the output side to a load of 25  $\Omega$  by a broadband matching network: Dimensioning of this network was based on a practical dummy transistor of 24  $\Omega$ //43 pF. The maximum VSWR measured within the band was 1.16.

At the input side tunable narrowband matching networks were applied at several frequencies. By tuning this amplifier for minimum return loss at  $P_O = 15$  W the powergain was measured directly.

For measurement of the input impedance the DC power, signal source and transistor were disconnected from the amplifier and the signal source circuit connection was terminated with 50  $\Omega$ . After that the impedance was measured at the gate connection of the transistor. The input impedance of the transistor is the conjugate of the measured impedance if the circuit doesn't contain resistive components.

This procedure was repeated at several frequencies in the band to get sufficient data for the design.

Figures 14, 15 and 16 present the data in graphical form.

#### 2.3 Output matching section

Because of the symmetrical set-up of this amplifier its matching sections can be divided into two equal parts. Each part belonging to one transistor. In the next discussion one half of the output matching section will be considered.

As mentioned in the previous section the optimum load resistance for  $P_O = 15$  W and  $V_{DS} = 28$  V is 26.1  $\Omega$  according to equation (1).

When two of these transistors are used in a push-pull configuration the optimum load resistance adds up to 52.2  $\Omega$ . This value is very close to 50  $\Omega$  to which these transistors have to be matched. So, if we choose the optimum load resistance to be 50  $\Omega$  we can suffice with a 1 : 1 balance to unbalance transformer.

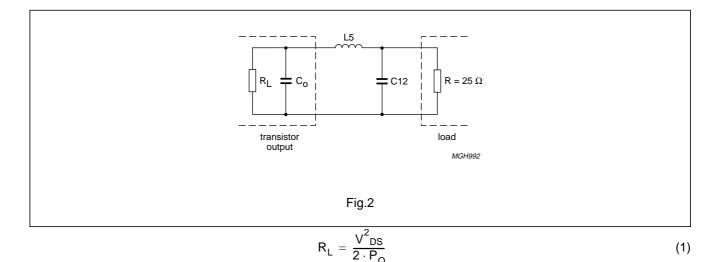

The output capacitance  $C_O$  of the transistor can be compensated over a certain bandwidth by absorbing it in a low-pass Chebyshev  $\pi$ -section, see Fig.2.

Application Note NCO8701

$R_L$  represents the optimum load resistance for the transistor. The components L5 and C12 can be determined with the following formulae if  $R_L = R$  and  $C_O = C12 = C$ :

The normalized value of C is:

$$A = \omega_{m} \cdot C \cdot R \tag{2}$$

in which  $\omega_m = 2 \times \pi \times f_{max}$

The normalized value of L5 can be calculated as follows:

$$B = \frac{\omega_{\mathsf{m}} \times \mathsf{L}_{\mathsf{5}}}{\mathsf{R}} \tag{3}$$

$$B = \frac{8 \times A}{3 \cdot A^2 + 4} \tag{4}$$

The maximum VSWR of this network follows from:

$$VSWR_{max} = \left\{ \frac{x^3 + 1}{x^3 - 1} \right\}^2$$

(5)

in which  $x = \gamma + (\gamma^2 + 1)^{1/2}$

and  $\gamma = 1/A$

For this section R = 25  $\Omega$  and C = 43 pF. This results in: A = 0.7430  $\rightarrow$  B = 1.0509  $\rightarrow$  L5 = 38 nH and VSWR<sub>max</sub> = 1.156.

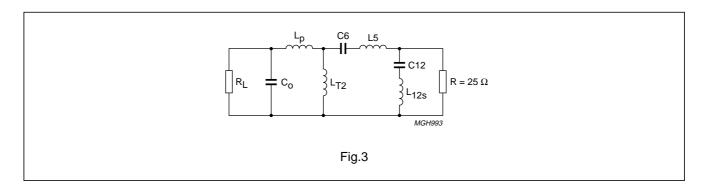

In practice this circuit comprises some additional components, see Fig.3.

#### These are:

$L_p$  – the parasitic drain and source inductance which has been accounted for by this way. Its value is approx. 1.4 nH  $L_{T2}$  – the drain choke inductance which equals approx. 0.8  $\mu$ H. Determination of this inductance will be treated in a later chapter.

L<sub>12S</sub> - the parasitic series inductance of C12, which is approx. 1 nH

C<sub>6</sub> – the DC-blocking capacitor which is also employed for low frequency compensation of L<sub>T2</sub>.

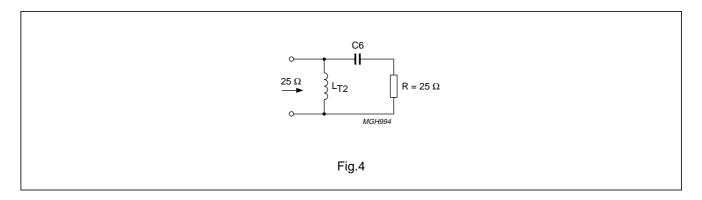

The value of  $C_6$  is calculated with the aid of the information given in ref.(1). The drain load circuit for low frequency is shown in Fig.4.

### Application Note NCO8701

Compensation according to ref.(1) gives at f = 25 MHz:

$$C_6 = 1.28 \text{ nF}$$

with VSWR<sub>max</sub> = 1.04

The circuit in Fig.3 was optimized for the frequency range 25-110 MHz. For this purpose a computer optimization program was used. The criterion used was for overall minimum VSWR with respect to 25  $\Omega$ .

The results before and after optimization are shown in Table 1.

Table 1

| BEFORE OPTIMIZATION |         | AF                  | AFTER OPTIMIZATION |  |  |

|---------------------|---------|---------------------|--------------------|--|--|

| C <sub>6</sub>      | 1.28 nF | C <sub>6</sub>      | 7.9 nF             |  |  |

| L <sub>5</sub>      | 38 nH   | L <sub>5</sub>      | 34.6 nH            |  |  |

| C <sub>12</sub>     | 43 pF   | C <sub>12</sub>     | 37.9 pF            |  |  |

| VSWR <sub>max</sub> | 1.169   | VSWR <sub>max</sub> | 1.098              |  |  |

### 2.4 Input matching section

The purpose of the input matching section is two-fold. First to match the transistor input impedance to the source impedance of 50  $\Omega$  with a sufficiently low VSWR across the frequency band. Second to compensate the variation in gain with frequency.

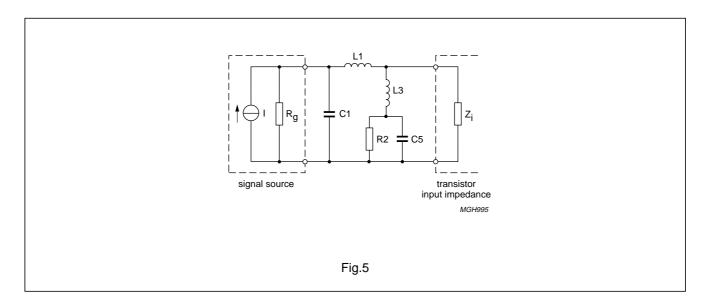

The input matching section chosen is depicted in Fig.5 for one transistor.

### Application Note NCO8701

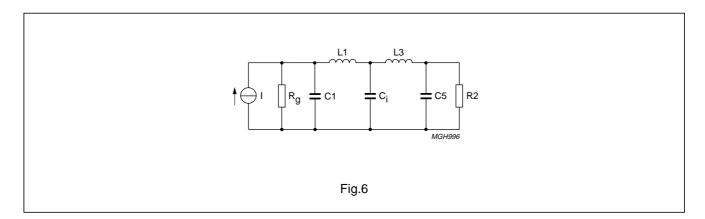

Since the input impedance of the transistor is strongly capacitive, Zi can be approximated by an ideal capacitor. This network can then be treated as a symmetrical double pi-section, see Fig.6.

In order to get sufficient gain flatness a constant voltage has to be developed across capacitor Ci. For optimum dimensioning of this network the following formulae are valid:

$$Rg = R2 = \frac{1.6}{\omega_{\rm m} \cdot ci}$$

(6)

$$C1 = C5 = 0.386 \times Ci \tag{7}$$

$$L1 = L3 = 0.997 \times \frac{Rg}{\omega_m} \tag{8}$$

in which  $\omega m$  is the maximum angular frequency. These formulae have been obtained by a computer optimization program which also indicates that the maximum voltage variation across Ci is  $\pm 0.36$  dB and the maximum VSWR seen by the generator 1.36. When the input capacitance at the lowest frequency is chosen, which is approx. 117 pF, we find that:

$$Rg = R2 = 19.8 \Omega$$

Application Note NCO8701

$$C1 = C5 = 45.2 \text{ pF}$$

$L1 = L3 = 28.6 \text{ nH}.$

In practice Rg is equal to 25  $\Omega$  and Zi varies with frequency. This required a re-optimization of this network with the actual values of Zi and Rg. The values calculated above were used as the initial values and parasitics of C1 and C5 were included. The target gain was set to 17.5 dB.

The results of this optimization are shown in Table 2.

Table 2

| BEFORE OPTIMIZATION |         | AF                  | AFTER OPTIMIZATION |  |  |

|---------------------|---------|---------------------|--------------------|--|--|

| C1                  | 45.2 pF | C1                  | 60.1 pF            |  |  |

| C5                  | 45.2 pF | C5                  | 47.5 pF            |  |  |

| L1                  | 28.6 nH | L1                  | 36 nH              |  |  |

| L3                  | 28.6 nH | L3                  | 43.8 nH            |  |  |

| R2                  | 19.8 Ω  | R2                  | 20.8 Ω             |  |  |

| Rg                  | 25 Ω    | Rg                  | 25 Ω               |  |  |

| VSWR <sub>max</sub> | 1.812   | VSWR <sub>max</sub> | 1.376              |  |  |

| G <sub>pmin</sub>   | 15.8 dB | G <sub>pmin</sub>   | 17.1 dB            |  |  |

| G <sub>pmax</sub>   | 16.9 dB | G <sub>pmax</sub>   | 17.9 dB            |  |  |

#### 3 TRANSFORMER DESIGN

#### 3.1 General

As mentioned before transformers employed at the input and output side utilize twisted-wire-pair transmission lines would on a toroidal core

The windings are uniformly distributed around the toroid. The required characteristic impedance of the transmission lines is 50  $\Omega$ . In practice Zo will differ from this required value and compensation measures will be necessary (2). This can be achieved with:

- Parallel capacitances across input and output terminals of the transformers if Zo > 50  $\Omega$

- Inductances in series with the input and output terminals of the transformer if Zo < 50  $\Omega$ .

The result of this compensation is an exact match at the maximum frequency. There will be however, a slight mismatch at low frequency which is many times smaller then that at the maximum frequency without compensation. Because the amount of HF compensation will depend on the circuit layout and the exact transformer construction no calculations will be made on this aspect of the transformers. The amount of compensation will be determined in the circuit by employing adjustable capacitors.

### 3.2 Design of the output transformer

The characteristic impedance of 50  $\Omega$  for the transmission line of the output transformer has been obtained with enamelled copper wire of 0.6 mm diameter. Its diameter with isolation included is 0.66 mm. The number of twists applied are 2 per centimeter.

A suitable core material for this frequency range is Philips 4C6 grade available in several sizes of toroid. The size of the toroid is determined by the maximum allowable dissipation which is limited to 350 mW/cm<sup>3</sup> to prevent excessive rise in temperature. Designing for a maximum of 1% power loss in the core (300 mW) the minimum effective volume required is:

$$Ve_{min} = \frac{P_{loss}}{350 \text{ mW/cm}^3} = \frac{300}{350} = 0.85 \text{ cm}^3$$

Application Note NCO8701

The smallest toroid that is suitable is a core with dimensions  $D \times d \times h = 23 \times 14 \times 7$  mm corresponding with a effective core volume of 1.79 cm<sup>3</sup>. As a result the core loss reduces to 170 mW/cm<sup>3</sup>.

According to reference (3) this corresponds to a maximum flux density (B) of 0.2 mT at 110 MHz. The required number of turns is determined by the ratio Rp/L in which  $R_p$  is the loss resistance that represents the core loss and L the inductance in parallel with the output terminals, see reference (4).

This ratio is equal to:

$$R_{p}/L = \frac{\omega^{2} \times B^{2} \times Ve}{2 \times \mu_{0} \times \mu_{r} \times P_{loss}}$$

(9)

which amounts to:

$$R_{p}/L = \frac{\left(2 \times \pi \times 110 \times 10^{6}\right)^{2} \times \left(0.2 \times 10^{-3}\right)^{2} \times 1.79 \times 10^{-6}}{2 \times 4 \times \pi \times 10^{-7} \times 120 \times 0.3} = 472 \Omega/\mu H$$

To keep the core loss below 1% we must keep the parallel loss resistance above 5000  $\Omega$  with reference to 50  $\Omega$ . This means an inductance of: L = Rp/472 = 10.6  $\mu$ H

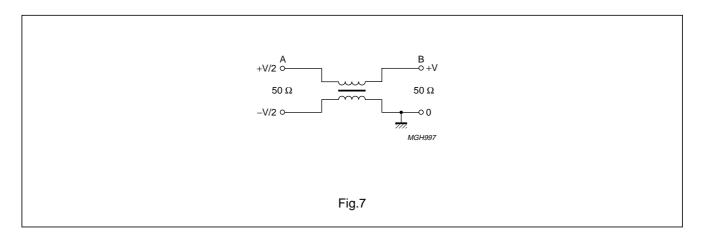

Between point A and B in Fig.7 the voltage is one half of the output voltage. Therefore the inductance between these points must be a quarter of that across the 50  $\Omega$  terminals, so:

$$L_{AB} = L/4 = 10.6/4 = 2.65 \,\mu H$$

The number of turns required can be calculated with the following formula (3):

$$L = A_L \times N^2 \tag{10}$$

$$A_{L} = \frac{0.4 \times \pi \times \mu r}{\Sigma I/A} \tag{11}$$

in which:

A<sub>L</sub> is the inductance in (nH)

$\Sigma$  /A is the core constant in (mm<sup>-1</sup>) given in (3)

N is the number of turns

μr is the relative permeability (120 for grade 4C6).

For a toroid of 23 mm the core constant is 1.81 mm<sup>-1</sup>. So, the inductance factor amounts to:

$$A_L = \frac{0.4 \times \pi \times 120}{1.81} = 83.3 \text{ nH}$$

Application Note NCO8701

and the required number of turns:

$$N = \sqrt{\frac{2.65 \times 10^3}{83.3}} = 5.6 \text{ turns}$$

In practice the number of turns will be 6, so the inductance in parallel with the output terminals rises to:

$$(6/5.6)^2 \times 10.6 = 12 \mu H$$

This corresponds to a reactance of 1885  $\Omega$  at 25 MHz which is high enough to be neglected.

The core loss reduces to:

$$(5.6/6)^2 \times 1\% = 0.87\%$$

The measured value of  $L_{AB}$  was approx. 3.5  $\mu H$ .

### 3.3 Design of the input transformer

The input transformer is of the same type as the output transformer and is also designed in the same way.

To obtain a characteristic impedance of 50  $\Omega$  for the windings enamelled Cu-wire with a bare diameter of 0.50 mm is used. The diameter with isolation included is 0.55 mm. The number of twists applied is  $2\frac{3}{4}$  per centimeter.

Allowing an input power level of 1.5 W the minimum effective volume for 1% power loss in the core is:

$$Ve_{min} = 15/350 = 0.043 \text{ cm}^3$$

The smallest toroid that suits our need is a type with dimensions  $D \times d \times h = 9 \times 6 \times 3$  mm. The effective core volume is 0.105 cm<sup>3</sup>, so the core loss reduces to 143 mW/cm<sup>3</sup>. This corresponds to a maximum flux density B of approx. 0.18 mT at f = 110 MHz according to ref.(3). The ratio Rp/L amounts to:

$$Rp/L = \frac{\left(2 \times \pi \times 110 \times 10^{6}\right)^{2} \times \left(0.18 \times 10^{-3}\right)^{2} \times 0.105 \times 10^{-6}}{2 \times 4 \times \pi \times 10^{-7} \times 120 \times 0.015} = 360\Omega/\mu H$$

For 1% loss L amount to:

$$L = Rp/360 = 5000/360 = 13.9 \mu H$$

$$L_{AB} = 13.9/4 = 3.48 \mu H$$

The required number of turns for a 9 mm toroid with a core constant of 5.17 mm<sup>-1</sup> is:

$$A_L = \frac{0.4 \times \pi \times 120}{5.17} = 29.2 \text{ nH}$$

$$N \ = \ \sqrt{\frac{3.48 \times 10^3}{29.2}} \ = \ 11 \ turns$$

An inductance of L =  $13.9 \,\mu\text{H}$  corresponds to a reactance of  $2183 \,\Omega$  at 25 MHz which is high enough to be neglected.

According to measurements 10 turns were sufficient to obtain  $L_{AB} \approx 3.5 \mu H$ .

#### 3.4 The tapped choke (T2)

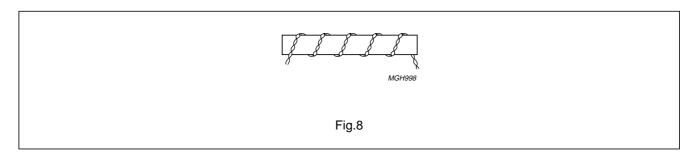

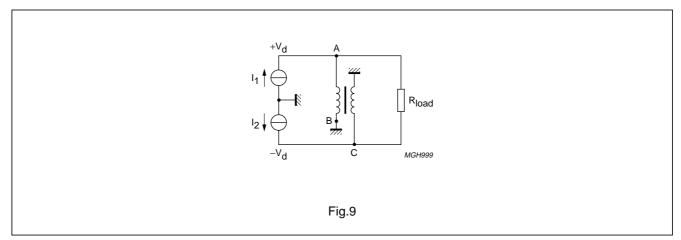

The chokes in the drain circuits are wound on a common ferrite rod. The windings are twisted together. Constructional details are shown in Fig.8. With this arrangement the dc flux components in the core cancel out and a much smaller component results. Because a rod has a open magnetic circuit saturation effects will hardly occur. In Fig.9 the output part of the amplifier is given in a different way.

### Application Note NCO8701

The current sources have a frequency spectrum in which the even order components are in phase and the odd order ones in anti-phase.

For the even harmonics the impedance between point A and C will depend on the coupling factor K between the windings with:

$$\omega L_{AB} (1 - K) \tag{12}$$

If the coupling factor amounts to 1 points A and C will be short circuited. If the current components are in anti-phase the total inductance between these points shunts the load resistance. Because the voltage between point A and B is equal to  $\frac{1}{2}$  V<sub>AC</sub> the total inductance L<sub>AC</sub> is equal to 4 L<sub>AB</sub> if the coupling factor is 1.

The reactance of this shunting inductance is allowed to be at least 4 times the load resistance or 200  $\Omega$  at 25 MHz. So, L<sub>AC</sub> amounts to 1.27  $\mu$ H and L<sub>AB</sub> to 0.318  $\mu$ H.

To obtain the inductance  $L_{AB}$  a ferrite rod grade 4B1 has been used with a length of 30 mm and a diameter of 5 mm. According to ref.(3) its relative permeability is equal to 20. The number of turns can be determined with:

$$N = \sqrt{\frac{L \times I}{\mu o \times \mu r \times A}}$$

(13)

For LAB this amount to:

$$N = \sqrt{\frac{0.318 \times 10^{-6} \times 30 \times 10^{-3}}{4 \times \pi \times 10^{-7} \times 1/4 \times \pi \times (5 \times 10^{-3})^2}} = 4.4 \text{ turns}$$

In practice 5 turns will be used so  $L_{AC}$  will be equal to 1.6  $\mu$ H. The measured value for  $L_{AB}$  was 0.48  $\mu$ H at 25 MHz. The windings are constructed of enamelled copper wire of 0.8 mm diameter.

Application Note NCO8701

#### 4 AMPLIFIER CONSTRUCTION

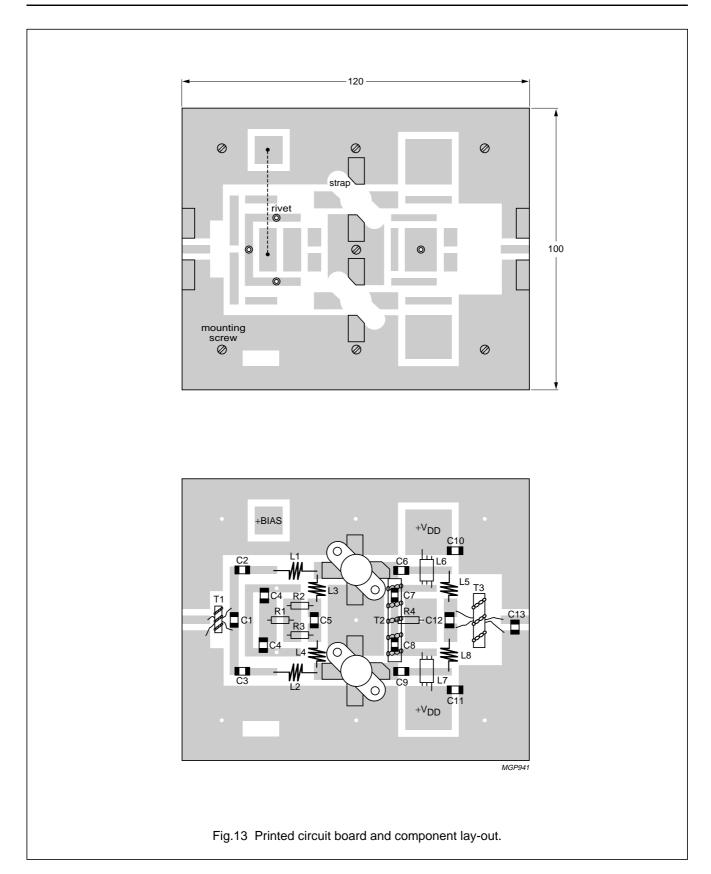

#### 4.1 Printed circuit board and component layout

The printer circuit board of this amplifier is made of two-sided copper clad epoxy fibre glass ( $\varepsilon r = 4.5$ ) laminate of 1/16" thickness.

Circuit components are situated on one side of this board, the other side serves as ground plane. A full sized pattern of the printed circuit board and component layout is given in Fig.13. The parasitic inductance of the printed tracks are absorbed in the inductances of the matching networks. Connections to the ground plane are made by means of tubular rivets, straps under the source leads and at the N-connectors and the mounting screws.

#### 4.2 Heatsink

The printed circuit board is attached to a solid copper plate, with dimensions  $120 \times 100 \times 10$  mm, which functions as a heatsink. It is provided with a tube in order to control its temperature by means of a water cooling system. Good thermal contacts between transistors and heatsink is obtained by use of a heat-sinking compound.

#### 5 AMPLIFIER ALIGNMENT

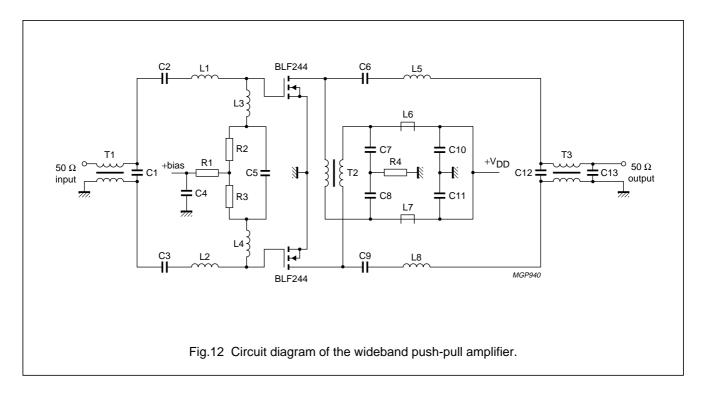

The amplifier was constructed according to the theoretical design procedures. Figure 12 shows the total circuit diagram of this amplifier. Parallel matching components as C1, C5 and C12 are connected directly from one side of the circuit to the other. Therefore their values are exactly one half of those calculated. The component list is given in Table 4.

Alignment of this amplifier was first done on a small signal basis. First the output circuit was aligned by replacing the BLF244 transistors with dummy loads, representing the conjugate of the optimum load impedance. The dummy's consisted of a 25  $\Omega$  resistance and a 43 pF capacitance. Several components in parallel were used to obtain symmetry and to reduce parasitic inductances. These components were soldered in an empty SOT123 header. The return loss was measured versus frequency at the load connection of the amplifier and minimized by applying compensation capacitors between the terminals of the output transformer. At the load site of the transformer 3.6 pF (C13) was needed and at the transistor side C12 was increased from 20 to 22 pF. The maximum VSWR obtained was 1.22.

Alignment of the input circuit has been done with the transistors in the circuit and supply and load connected. The quiescent drain current was set to approx. 200 mA per transistor and return loss was measured versus frequency. Experiments with capacitors in parallel with the input transformer terminals showed that no compensation was needed. The maximum VSWR obtained was 1.30.

After the small signal alignment the transistors were set to class-B operation by decreasing the quiescent drain current to 25 mA.

The first results obtained at Pout = 30 W were:

Gp = 15.6  $\pm$ 1.2 dB; Eff. = 61.3  $\pm$ 10%; VSWR  $\leq$  1.40 and second harmonic level  $\leq$  -33 dB.

In order to improve the total performance of this amplifier especially with respect to gain flatness, variation in efficiency and second harmonic level some minor changes were introduced in the amplifier.

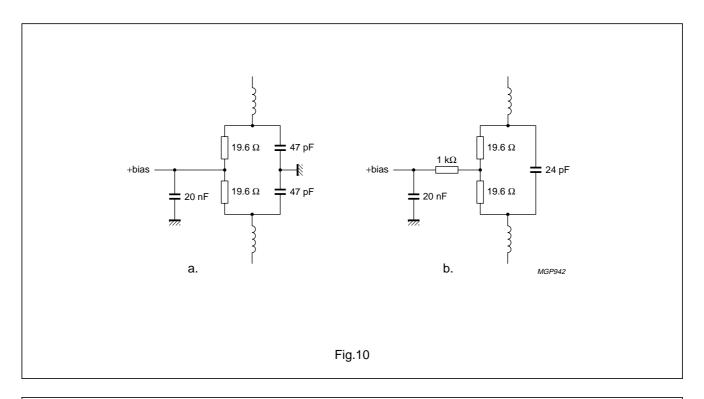

1. At the input side the circuit configuration shown in Fig.10a was changed into that of Fig.10b. No appreciable improvement was achieved with respect to gain performance but variations in efficiency reduced to ±6%. However, at the lower side of the band the second harmonic level increased to –28 dB.

### Application Note NCO8701

- 2. Raising the quiescent drain current to 50 mA improved the gain with approx. 0.3 dB. However, the efficiency decreased with approx. 0.8%.

- A resistance of approx. 12 Ω from the mid tap of the drain choke T2 to ground instead of direct grounding increased the average efficiency with approx. 1% and its variations decreased to ±2.8%. The second harmonic level improved with 2 dB.

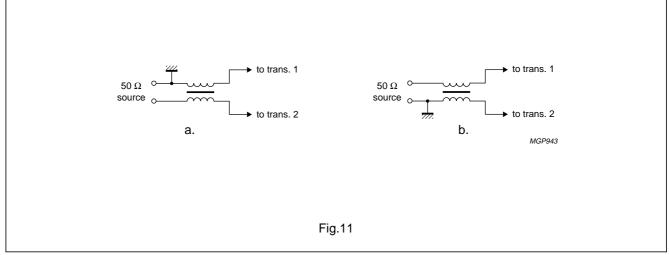

- 4. The input balun was originally connected as shown in Fig.11a. For a perfect symmetrical push-pull amplifier it does not matter which terminal is grounded. In this case exchange of the terminals strongly affected the second harmonic level. For the case of Fig.11b this level improved to < -40 dB.</p>

- 5. Finally the value of the resistors shown in Fig.10 was increased to 23.7  $\Omega$ . This improved the gain flatness to approx.  $\pm 0.6$  dB. The input VSWR increased to 1.5.

Application Note NCO8701

#### 6 AMPLIFIER PERFORMANCE

#### 6.1 General

Measurement of the amplifier performance was carried out under nominal conditions unless stated otherwise. These conditions are:

Supply voltage  $V_{dd} = 28 \text{ V}$

Quiescent drain current I<sub>dq</sub> = 50 mA

Heatsink temperature T<sub>hs</sub> = 25 °C.

Measurements were done at 10 frequencies within the band and 2 frequencies outside the band.

The BLF244 samples used, are matched on their threshold voltage V. The measured parameters of these transistors which can be relevant for balanced operation are given in Table 3.

#### Table 3

| PARAMETER        | CONDITIONS                                                       | UNIT | T1   | T2   |

|------------------|------------------------------------------------------------------|------|------|------|

| V <sub>T</sub>   | $V_{ds} = 10 \text{ V}; I_{d} = 5 \text{ mA}$                    | V    | 3.14 | 3.14 |

| G <sub>FS</sub>  | $V_{ds} = 10 \text{ V}; I_{d} = 750 \text{ mA}$                  | mS   | 794  | 838  |

| C <sub>rss</sub> | $V_{ds} = 28 \text{ V}; V_{gs} = 0 \text{ V}; f = 1 \text{ MHz}$ | pF   | 4.46 | 4.21 |

The largest asymmetry observed in the drain current was  $\pm 3\%$  at f = 25 MHz and P<sub>o</sub> = 30 W.

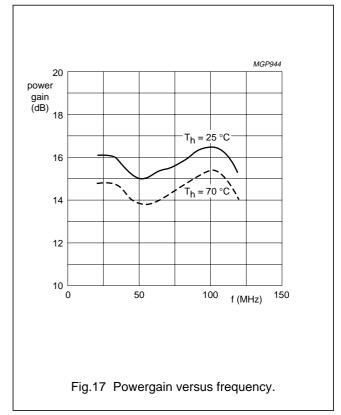

### 6.2 Performance at constant output power

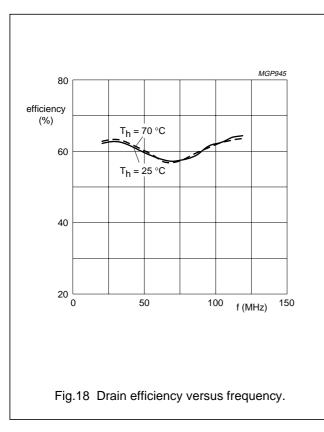

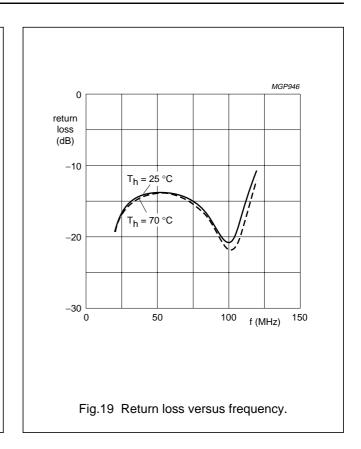

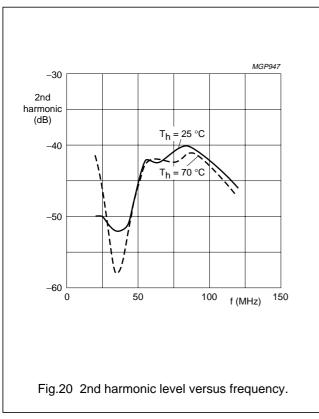

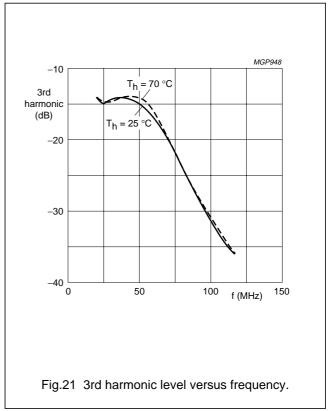

Measurements of the performance at a constant output power of 30 W were carried out at two heatsink temperatures, viz.  $T_h = 25$  and 70 °C.

The results obtained are:

Powergain =  $15.7 \pm 0.7$  dB, see Fig.17

Drain eff. =  $60.6 \pm 3.3\%$ , see Fig.18

Input return loss <-14 dB (VSWR <1.50), see Fig.19

Second harmonic level <-40 dB, see Fig.20

Third harmonic level <-14 dB, see Fig.21.

At  $T_h = 70$  °C the powergain decreased with approx. 1.2 dB see Fig.17.

The other parameters showed no appreciable change.

### 6.3 Performance at constant input power

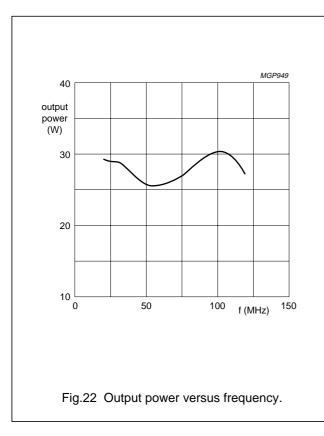

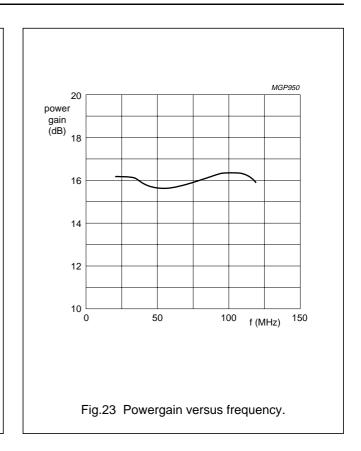

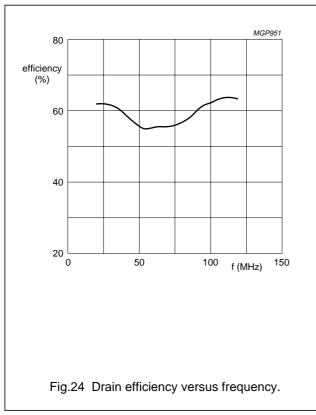

Performance of this amplifier was also measured at a constant input power of 700 mW. The result obtained are:

Output power =  $27.9 \pm 2.3$  W, see Fig.22

Power gain =  $16.0 \pm 0.3$  dB, see Fig.23

Drain eff. =  $59.0 \pm 4.5\%$ , see Fig.24.

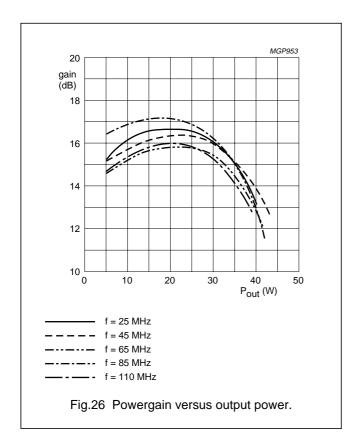

#### 6.4 Performance at constant frequency

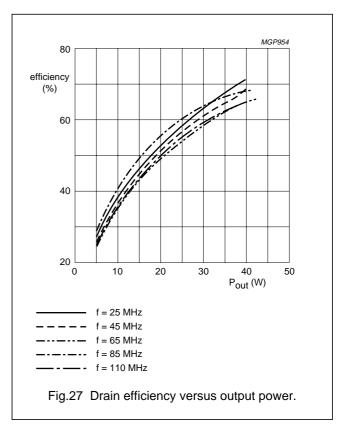

Figures 25, 26 and 27 show the following curves measured at 5 different frequencies:

$$P_0 = f(P_i)$$

$$G_p = f(P_o)$$

Eff. =

$$f(P_0)$$

.

Application Note NCO8701

#### 7 CONCLUSIONS

Using two BLF244 MOS transistors (matched on threshold voltage) in a push-pull configuration approx. 16 dB power gain and 60% drain efficiency have been obtained for an output power of 30 W, when operated with a quiescent drain current of 50 mA per transistor at  $V_{ds}$  = 28 V. The largest asymmetry observed in the drain current was  $\pm 3\%$  at  $P_{out}$  = 30 W and f = 25 MHz. The input VSWR was below 1.5.

Throughout the band the second harmonic level was lower than –40 dB with reference to the fundamental. At a heatsink temperature of 70 °C the powergain decreased with approximately 1 dB while the other parameters showed no appreciable change.

### 8 REFERENCES

- H. Nielinger: 'Optimale dimensionerung von Breitbandanpassungsnetwerken'; N.T.Z. 1968, Heft 2, p.p. 88-91

- 2. A.H. Hilbers: 'Design of HF wideband power transformers'; Philips Applications information ECO6907, 1970

- 3. Philips Data Handbook: 'MA01 on Magnetic Products: Soft Ferrites. For power handling of 4C6 material. See also earlier version of this handbook.

- 4. A.H. Hilbers; 'Power transformers for the frequency range of 30 80 MHz'; Laboratory report ECO7703, 1977.

Application Note NCO8701

Table 4 List of components

| ·                                   |                                                                                                                                                                                         |  |  |  |

|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Capacitors                          |                                                                                                                                                                                         |  |  |  |

| C1 = 30 pF                          | multilayer ceramic chip capacitor; note 1                                                                                                                                               |  |  |  |

| C2 = C3 = C6 = C7 = C8 = C9 = 10 nF | multilayer ceramic capacitor (cat.nr. 2222 852 47103)                                                                                                                                   |  |  |  |

| C4 = 2 × 10 nF                      | multilayer ceramic chip capacitor (cat.nr. 2222 852 47103)                                                                                                                              |  |  |  |

| C5 = 24 pF                          | multilayer ceramic chip capacitor; note 1                                                                                                                                               |  |  |  |

| C10 = C11 = 100 nF                  | multilayer ceramic chip capacitor (cat.nr. 2222 852 47104)                                                                                                                              |  |  |  |

| C12 = 22 pF                         | multilayer ceramic chip capacitor; note 1                                                                                                                                               |  |  |  |

| C13 = 3.6 pF                        | multilayer ceramic chip capacitor; note 1                                                                                                                                               |  |  |  |

| Inductors                           |                                                                                                                                                                                         |  |  |  |

| L1 = L2 = 27 nH                     | 3 turns enamelled Cu-wire (0.8 mm); int.dia. = 4.0 mm; length = 6.1 mm; leads $2 \times 3$ mm                                                                                           |  |  |  |

| L3 = L4 = 48 nH                     | 4 turns enamelled Cu-wire (0.8 mm); int.dia = 4.0 mm; length 6.2 mm; leads $2 \times 1$ mm                                                                                              |  |  |  |

| L5 = L8 = 30 nH                     | 3 turns enamelled Cu-wire (0.8 mm); int.dia. = 4.0 mm; length = 4.8 mm; leads $2 \times 2$ mm                                                                                           |  |  |  |

| L6 = L7 = Ferroxcube RF choke       | grade 3B (cat.nr. 4312 020 36640)                                                                                                                                                       |  |  |  |

| Resistors                           |                                                                                                                                                                                         |  |  |  |

| R1 = 1 kΩ                           | metal film resistor; 0.4 W                                                                                                                                                              |  |  |  |

| R2 = R3 = 23.7 Ω                    | metal film resistor; 0.4 W                                                                                                                                                              |  |  |  |

| R4 = 12.1 Ω                         | metal film resistor; 0.4 W                                                                                                                                                              |  |  |  |

| Transformers                        |                                                                                                                                                                                         |  |  |  |

| T1- 1/1 Balun                       | 10 turns of twisted pair of 0.5 mm enamelled Cu-wire ( $2^{3}/_{4}$ twists per cm) wound on a toroidal core grade 4C6, dimensions ( $9 \times 6 \times 3$ ) mm (cat.nr. 4322 020 97191) |  |  |  |

| T2- Drain choke                     | 5 turns of twisted pair of enamelled Cu-wire (4.5 twists per cm) wound on a ferroxcube rod grade 4B1, dimensions ( $5 \times 30$ ) mm                                                   |  |  |  |

| T3- 1/1 Balun                       | 6 turns of twisted pair of 0.6 mm enamelled Cu-wire (2 twists per cm) wound on a toroidal core grade 4C6, dimensions ( $23 \times 14 \times 7$ ) mm (cat.nr. 4322 020 97171)            |  |  |  |

| Printed circuit board               | double sided Cu-clad epoxy fibreglass laminate (εr = 4.5), thickness 1/16"                                                                                                              |  |  |  |

|                                     |                                                                                                                                                                                         |  |  |  |

### Note

1. American Technical Ceramics capacitor type 100B.

Application Note NCO8701

Application Note NCO8701

### Application Note NCO8701

### Application Note NCO8701

## Application Note NCO8701

### Philips Semiconductors – a worldwide company

Argentina: see South America

Australia: 34 Waterloo Road, NORTH RYDE, NSW 2113,

Tel. +61 2 9805 4455, Fax. +61 2 9805 4466

Austria: Computerstr. 6, A-1101 WIEN, P.O. Box 213, Tel. +43 160 1010,

Fax. +43 160 101 1210

**Belarus:** Hotel Minsk Business Center, Bld. 3, r. 1211, Volodarski Str. 6, 220050 MINSK, Tel. +375 172 200 733, Fax. +375 172 200 773

**Belgium:** see The Netherlands **Brazil:** see South America

Bulgaria: Philips Bulgaria Ltd., Energoproject, 15th floor,

51 James Bourchier Blvd., 1407 SOFIA, Tel. +359 2 689 211, Fax. +359 2 689 102

Canada: PHILIPS SEMICONDUCTORS/COMPONENTS,

Tel. +1 800 234 7381

China/Hong Kong: 501 Hong Kong Industrial Technology Centre,

72 Tat Chee Avenue, Kowloon Tong, HONG KONG,

Tel. +852 2319 7888, Fax. +852 2319 7700

Colombia: see South America

Czech Republic: see Austria

Denmark: Prags Boulevard 80, PB 1919, DK-2300 COPENHAGEN S,

Tel. +45 32 88 2636, Fax. +45 31 57 0044 **Finland:** Sinikalliontie 3, FIN-02630 ESPOO, Tel. +358 9 615800, Fax. +358 9 61580920

France: 51 Rue Carnot, BP317, 92156 SURESNES Cedex,

Tel. +33 1 40 99 6161, Fax. +33 1 40 99 6427

Germany: Hammerbrookstraße 69, D-20097 HAMBURG,

Tel. +49 40 23 53 60, Fax. +49 40 23 536 300

Greece: No. 15, 25th March Street, GR 17778 TAVROS/ATHENS,

Tel. +30 1 4894 339/239, Fax. +30 1 4814 240

Hungary: see Austria

India: Philips INDIA Ltd, Band Box Building, 2nd floor, 254-D, Dr. Annie Besant Road, Worli, MUMBAI 400 025,

Tel. +91 22 493 8541, Fax. +91 22 493 0966

Indonesia: see Singapore

Ireland: Newstead, Clonskeagh, DUBLIN 14, Tel. +353 1 7640 000, Fax. +353 1 7640 200

Israel: RAPAC Electronics, 7 Kehilat Saloniki St, PO Box 18053, TEL AVIV 61180, Tel. +972 3 645 0444, Fax. +972 3 649 1007

Italy: PHILIPS SEMICONDUCTORS, Piazza IV Novembre 3, 20124 MILANO, Tel. +39 2 6752 2531, Fax. +39 2 6752 2557

Japan: Philips Bldg 13-37, Kohnan 2-chome, Minato-ku, TOKYO 108,

Tel. +81 3 3740 5130, Fax. +81 3 3740 5077

**Korea:** Philips House, 260-199 Itaewon-dong, Yongsan-ku, SEOUL, Tel. +82 2 709 1412, Fax. +82 2 709 1415

**Malaysia:** No. 76 Jalan Universiti, 46200 PETALING JAYA, SELANGOR, Tel. +60 3 750 5214, Fax. +60 3 757 4880

Mexico: 5900 Gateway East, Suite 200, EL PASO, TEXAS 79905,

Tel. +9-5 800 234 7381 **Middle East:** see Italy

Netherlands: Postbus 90050, 5600 PB EINDHOVEN, Bldg. VB,

Tel. +31 40 27 82785, Fax. +31 40 27 88399

New Zealand: 2 Wagener Place, C.P.O. Box 1041, AUCKLAND,

Tel. +64 9 849 4160, Fax. +64 9 849 7811 **Norway:** Box 1, Manglerud 0612, OSLO, Tel. +47 22 74 8000, Fax. +47 22 74 8341

**Philippines:** Philips Semiconductors Philippines Inc., 106 Valero St. Salcedo Village, P.O. Box 2108 MCC, MAKATI, Metro MANILA, Tel. +63 2 816 6380, Fax. +63 2 817 3474

**Poland:** Ul. Lukiska 10, PL 04-123 WARSZAWA, Tel. +48 22 612 2831, Fax. +48 22 612 2327

Portugal: see Spain Romania: see Italy

Russia: Philips Russia, Ul. Usatcheva 35A, 119048 MOSCOW,

Tel. +7 095 755 6918, Fax. +7 095 755 6919

Singapore: Lorong 1, Toa Payoh, SINGAPORE 1231,

Tel. +65 350 2538, Fax. +65 251 6500

Slovakia: see Austria Slovenia: see Italy

South Africa: S.A. PHILIPS Pty Ltd., 195-215 Main Road Martindale,

2092 JOHANNESBURG, P.O. Box 7430 Johannesburg 2000,

Tel. +27 11 470 5911, Fax. +27 11 470 5494 **South America:** Al. Vicente Pinzon, 173, 6th floor,

04547-130 SÃO PAULO, SP, Brazil, Tel. +55 11 821 2333, Fax. +55 11 821 2382

**Spain:** Balmes 22, 08007 BARCELONA, Tel. +34 3 301 6312, Fax. +34 3 301 4107

Sweden: Kottbygatan 7, Akalla, S-16485 STOCKHOLM,

Tel. +46 8 632 2000, Fax. +46 8 632 2745

**Switzerland:** Allmendstrasse 140, CH-8027 ZÜRICH, Tel. +41 1 488 2686, Fax. +41 1 488 3263

Taiwan: Philips Semiconductors, 6F, No. 96, Chien Kuo N. Rd., Sec. 1,

TAIPEI, Taiwan Tel. +886 2 2134 2865, Fax. +886 2 2134 2874 Thailand: PHILIPS ELECTRONICS (THAILAND) Ltd.,

209/2 Sanpavuth-Bangna Road Prakanong, BANGKOK 10260,

Tel. +66 2 745 4090, Fax. +66 2 398 0793

Turkey: Talatpasa Cad. No. 5, 80640 GÜLTEPE/ISTANBUL,

Tel. +90 212 279 2770, Fax. +90 212 282 6707

Ukraine: PHILIPS UKRAINE, 4 Patrice Lumumba str., Building B, Floor 7,

252042 KIEV, Tel. +380 44 264 2776, Fax. +380 44 268 0461

**United Kingdom:** Philips Semiconductors Ltd., 276 Bath Road, Hayes, MIDDLESEX UB3 5BX, Tel. +44 181 730 5000, Fax. +44 181 754 8421

United States: 811 East Arques Avenue, SUNNYVALE, CA 94088-3409,

Tel. +1 800 234 7381

Uruguay: see South America

Vietnam: see Singapore

Yugoslavia: PHILIPS, Trg N. Pasica 5/v, 11000 BEOGRAD,

Tel. +381 11 625 344, Fax.+381 11 635 777

**For all other countries apply to:** Philips Semiconductors, International Marketing & Sales Communications, Building BE-p, P.O. Box 218, 5600 MD EINDHOVEN, The Netherlands, Fax. +31 40 27 24825

© Philips Electronics N.V. 1998 SCA57

All rights are reserved. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner.

The information presented in this document does not form part of any quotation or contract, is believed to be accurate and reliable and may be changed without notice. No liability will be accepted by the publisher for any consequence of its use. Publication thereof does not convey nor imply any license under patent- or other industrial or intellectual property rights.

Printed in The Netherlands

Date of release: 1998 Mar 23

Internet: http://www.semiconductors.philips.com